## Xenon Photoflash Capacitor Charge with Photo Sense Interface

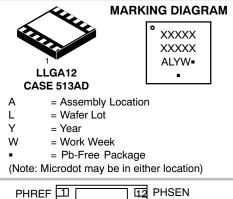

The NCP5080 product is a high voltage boost driver dedicated to the Xenon power flashes.

The built-in DC/DC converter is based on a flyback structure with an external transformer to adapt any range of high voltage demand. The external feedback network makes it possible to dynamically adjust of the output voltage.

#### Features

- 2.7 V to 5.5 V Input Voltage Range

- Xenon Function Fully Supported

- Built-in Short Circuit Protection

- Dedicated Photo Flash Trigger Pin

- Provides IGBT drive

- Embedded Photodiode Sense

- Adjustable Primary Ipeak Current

- This is a Pb-Free Device

#### **Typical Applications**

- Digital Camera Photo Flash

- Digital Cellular Phone Camera Photo Flash

- Low Power Beacon

#### http://onsemi.com

| PHREF | ш | 12 | PHSEN |

|-------|---|----|-------|

| TRGFL | 2 | 11 | VHB   |

| IGBT  | 3 | 10 | IPKRF |

| VBAT  | 4 | 9  | AGND  |

| PGND  | 5 | 8_ | READY |

| VSW   | 6 |    | EN    |

|       |   |    |       |

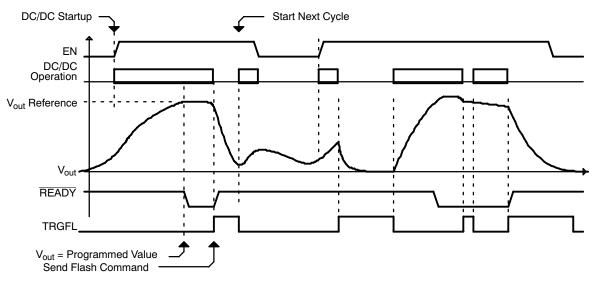

#### **ORDERING INFORMATION**

| Device       | Package   | Shipping <sup>†</sup> |

|--------------|-----------|-----------------------|

| NCP5080MUTXG | LLGA12    | 3000 / Tape & Reel    |

|              | (Pb-Free) |                       |

<sup>+</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

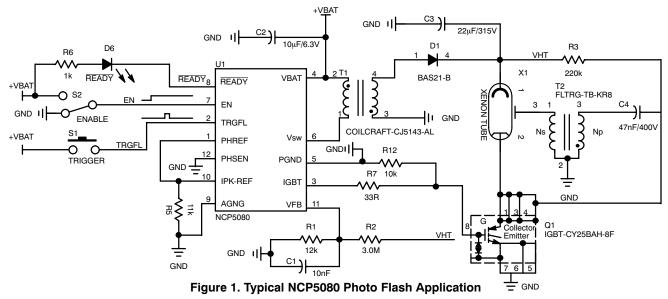

Figure 2. NCP5080 Simplified Block Diagram

### **PIN DESCRIPTIONS**

| PIN | Name   | Туре               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PHREF  | INPUT,<br>ANALOG   | The external controller biases this pin with the reference voltage used, together with the PHSEN pin, to control the illumination of the photo scene. The V <sub>PH</sub> voltage shall be in the 0.5 V to 1.5 V range, capable to support the internal resistor network (R load minimum is 500 k $\Omega$ ). The photo sense function is deactivated when 0.5 V $\leq$ PHREF $\leq$ 1.5 V and PHSEN = GND (see Table 4).                                                                                                                                                                                     |

| 2   | TRGFL  | INPUT,<br>DIGITAL  | A positive going pulse applied to this pin triggers the external IGBT and the flash sequence takes place. This command is active when EN = High, but is not synchronized with the output voltage value (see Table 4).                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | IGBT   | OUTPUT,<br>POWER   | This pin provides the signal to drive the external IGBT and can be forced High or Low independ-<br>ently of the output voltage value, (assuming EN = High) according to the TRGFL pin status (see<br>Table 4). Depending upon the type of IGBT used in the application, specific external gate network<br>might be necessary to satisfy the IGBT gate drive conditions.                                                                                                                                                                                                                                       |

| 4   | VBAT   | INPUT,<br>POWER    | This pin carries the power supply to the analog, digital and DC/DC converter blocks and must be decoupled to ground by a 10 $\mu F$ ceramic capacitor connected as close as possible to the package.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5   | PGND   | POWER              | This pin is the GROUND return for the DC/DC converter and must be connected to the system ground, a ground plane is strongly recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6   | VSW    | OUTPUT,<br>POWER   | This pin is the drain of the internal NMOS device and shall be connected to the primary of the external transformer. Care must be observed, at PCB layout level, to minimize the noise due to the large current and voltage transients present on that pin during normal operation.                                                                                                                                                                                                                                                                                                                           |

| 7   | EN     | INPUT,<br>DIGITAL  | This pin controls the operation of the boost converter:<br>$EN = Low \rightarrow$ The DC/DC converter is OFF, no flash can take place, the voltage across the<br>external reservoir capacitor depends solely upon the leakage current present in the environment.<br>$EN = High \rightarrow$ The DC/DC converter is activated, the voltage across the external reservoir<br>capacitor is regulated at the predetermined value according to the V <sub>FB</sub> reference. Similarly, a flash<br>can take place, assuming the Xenon tube is properly biased.                                                   |

| 8   | READY  | OUTPUT,<br>DIGITAL | This Open Drain Output goes LOW when the output voltage has reached the predetermined value across the external reservoir capacitor. The signal is HIGH when $V_{out}$ is below the expected value, or if a fault has been detected at chip level.                                                                                                                                                                                                                                                                                                                                                            |

| 9   | AGND   | POWER              | This pin returns the Analog and Digital blocks ground and must be connected to the external ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10  | IPKREF | INPUT,<br>ANALOG   | This pin provides the setup of the peak current flowing into the primary of the external transformer.<br>The main purpose of this reference is to adjust the size of the transformer as a function of the flash power.                                                                                                                                                                                                                                                                                                                                                                                        |

| 11  | VFB    | input,<br>Analog   | This pin is the voltage feedback used to regulate the high voltage across the external reservoir capacitor. The impedance across $V_{FB}$ and GND shall be kept to the lowest possible value to minimize the noise pickup.                                                                                                                                                                                                                                                                                                                                                                                    |

| 12  | PHSEN  | INPUT,<br>ANALOG   | This pin provides a feedback from the illumination during the photo flash and, associated to the PHREF signal, controls the duration of the photo flash. The photodiode, connected across PHSEN and VBAT, shall be adjusted according to the Xenon flash in use. On the other hand, an external pulldown resistor shall be connected between the PHSEN pin and the ground reference. Such a resistor shall be calculated to cope with the type of photodiode used in the illumination sense loop. The photo sense function is deactivated when PHSEN = GND and 0.5 V $\leq$ PHREF $\leq$ 1.5 V (see Table 4). |

1. Using low ESR ceramic capacitor, X5R type, is mandatory to optimize the DC/DC operation and to reduce the EMI.

#### MAXIMUM RATINGS (Note 2)

| Symbol                                                                                                                                                                           | Rating                                                    | Value                            | Unit               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------|--------------------|

| $V_{BAT,} V_{CC}$                                                                                                                                                                | Power Supply                                              | -0.3 < V <sub>BAT</sub> < 7.0    | V                  |

| V <sub>SW</sub>                                                                                                                                                                  | Output Power Supply                                       | 40.0                             | V                  |

| EN, PFLASH                                                                                                                                                                       | Digital Input Voltage<br>Digital Input Current            | -0.3 < V < V <sub>BAT</sub><br>1 | V<br>mA            |

| ESD Human Body Model: R=1500 Ω, C=100 pF (Note 3)<br>Machine Model                                                                                                               |                                                           | 2<br>200                         | kV<br>V            |

| PD EVALUATE POWER Dissipation @ T <sub>A</sub> = +85°C (Note 4)<br>R <sub>THja</sub> Thermal Resistance Junction-to-Air<br>R <sub>THJC</sub> Thermal Resistance Junction-to-Case |                                                           | 400<br>100<br>12                 | mW<br>°C/W<br>°C/W |

| T <sub>A</sub>                                                                                                                                                                   | Operating Ambient Temperature Range                       | -40 to +85                       | °C                 |

| TJ                                                                                                                                                                               | Operating Junction Temperature Range                      | -40 to +125                      | °C                 |

| T <sub>Jmax</sub>                                                                                                                                                                | Maximum Junction Temperature                              | +150                             | °C                 |

| T <sub>stg</sub>                                                                                                                                                                 | Storage Temperature Range                                 | -65 to + 150                     | °C                 |

|                                                                                                                                                                                  | Latchup Current Maximum Rating per JEDEC Standard: JESD78 | ±100                             | mA                 |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

2. Maximum electrical ratings define the values beyond which permanent damage(s) may occur internally to the chip whatever be the operating temperature

This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22-A114 Machine Model (MM) ±200 V per JEDEC standard: JESD22-A115

4. The maximum package power dissipation limit must not be exceeded.

5. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

**POWER SUPPLY SECTION** (Typical values are referenced to  $T_A = +25^{\circ}$ C, minimum and maximum values are referenced -40°C to +85°C ambient temperature, unless otherwise noted, and operating conditions are 2.85 V < V<sub>BAT</sub> < 5.5 V, unless otherwise noted)

| Pin | Symbol              | Rating                                                                                                                                      | Min | Тур      | Max       | Unit |

|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------|------|

| 4   | V <sub>BAT</sub>    | DC/DC Converter Power Supply                                                                                                                | 2.7 |          | 5.5       | V    |

| 4   | U <sub>VLO</sub>    | Input Voltage Undervoltage Monitoring                                                                                                       | 2.1 |          | 2.6       | V    |

| 6   | I <sub>pk</sub>     | Primary Transformer Peak Current (750 mA Final Test Correlation) $R_{ipk}$ = 11 $k\Omega$                                                   |     |          | 1.5       | A    |

| 6   | I <sub>dss</sub>    | Internal Power Switch NMOS Leakage Current<br>@ V <sub>dss</sub> = 40 V                                                                     |     |          | 0.5       | μΑ   |

|     | t <sub>start</sub>  | DC/DC Start Time ( $C_{out}$ = 100 $\mu$ F, No Load)<br>V <sub>BAT</sub> = 4 V, from EN Positive Pulse to V <sub>out</sub> = 300 V (Note 6) |     | 2        | 3         | S    |

| 4   | I <sub>stdb</sub>   | Standby Current,<br>V <sub>BAT</sub> = 5.5 V, $I_{out}$ = 0 mA, EN = Low<br>V <sub>BAT</sub> = 3.6 V, $I_{out}$ = 0 mA, EN = Low            |     |          | 1<br>0.75 | μΑ   |

| 4   | I <sub>op</sub>     | Operating Current,<br>@V <sub>out</sub> = Nominal, V <sub>BAT</sub> = 3.6 V, EN = High                                                      |     | 0.5      |           | mA   |

| 3   | R <sub>drv</sub>    | External IGBT Drive @ $V_{BAT}$ = 3.6V<br>$V_{gs}$ = High (Note 8)<br>$V_{gs}$ = Low                                                        |     | 23<br>33 | 37<br>52  | Ω    |

|     | T <sub>onmx</sub>   | Maximum Inductor Charge Current ON Time                                                                                                     |     | 60       |           | μS   |

|     | T <sub>offmx</sub>  | Maximum Inductor Discharge Current OFF Time                                                                                                 |     | 60       |           | μS   |

|     | T <sub>LEB</sub>    | Leading Blanking (Note 7)                                                                                                                   |     | 260      |           | ns   |

| 6   | R <sub>DS(on)</sub> | Internal Power Switch NMOS R <sub>DS(on)</sub><br>@ V <sub>BAT</sub> = 4.2 V                                                                |     | 250      | 600       | mΩ   |

6. Since this parameter is highly depending upon the application, it is not tested, guaranteed by design.

7. The blanking parameter is internal and cannot be tested in production, guaranteed by design.

Since the IGBT gate drive is derived from the V<sub>BAT</sub> supply, special care must be taken to ensure that the IGBT triggers when V<sub>gs</sub> is high and V<sub>BAT</sub> is below 3.0 V.

| Pin | Symbol                                                                | Rating                                                                                                                                                                                                                                                                  | Min   | Тур   | Max   | Unit |

|-----|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| 10  | I <sub>REF</sub>                                                      | Reference current @ $V_{REF}$ = 1.14 V (Notes 9 and 10)                                                                                                                                                                                                                 | 10    |       | 100   | μΑ   |

| 10  | V <sub>REF</sub>                                                      | Reference Voltage (Note 10)                                                                                                                                                                                                                                             | -3%   | 1.14  | +3%   | V    |

| 10  | I <sub>PKR</sub>                                                      | Reference Current (I <sub>REF</sub> ) Current Ratio                                                                                                                                                                                                                     | 12000 | 13700 | 15400 |      |

| 6   | F <sub>PWM</sub>                                                      | $ \begin{array}{l} \mbox{F}_{PWM} & \mbox{Internal DC/DC Flyback Frequency} \\ \hline (@ V_{BAT} = 4.2 \mbox{ V}, \mbox{ I}_p = 1 \mbox{ A}, \mbox{ Lp} = 6  \mbox{ H}, \mbox{ Lf} = 200 \mbox{ nH}, \\ \hline \mbox{Transformer} = TDK \mbox{ (Note 11)} \end{array} $ |       |       | 600   | kHz  |

| 11  | V <sub>FB</sub> Output Voltage Feed Back reference                    |                                                                                                                                                                                                                                                                         | 1.10  | 1.15  | 1.20  | V    |

| 1   | V <sub>PH</sub>                                                       | Photo Sense Voltage Reference                                                                                                                                                                                                                                           | 0.5   |       | 1.5   | V    |

| 1   | 1 V <sub>PHR</sub> Photo Reference Internal Resistance (Pin 1 to GND) |                                                                                                                                                                                                                                                                         |       | 625   |       | kΩ   |

|     | P <sub>FB</sub>                                                       | Photo Feedback Tolerance                                                                                                                                                                                                                                                |       | ±3    |       | %    |

| <b>ANALOG SECTION</b> (Typical values are referenced to $T_A = +25^{\circ}C$ , minimum and maximum values are referenced -40°C to +85°C |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| ambient temperature, unless otherwise noted, operating conditions 2.85 V < $V_{BAT}$ < 5.5 V, unless otherwise noted)                   |

9. I<sub>REF</sub> current specifies the reference current range one can absorb from the I<sub>REF</sub> pin

10. The external circuit must not force the  $I_{REF}$  pin voltage either higher or lower than the 1.14 V specified.

11. This parameter depends solely upon the output transformer and load characteristic and cannot be tested.

12. The overall photo sense tolerance depends upon the accuracy of the external resistor. Using 1% or better resistor is recommended.

| DIGITAL PARAMETERS SECTION (Typical values are referenced to T <sub>A</sub> = +25°C, minimum and maximum values are referenced               |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| -40 °C to +85°C ambient temperature, unless otherwise noted, operating conditions 2.85 V < V <sub>BAT</sub> < 5.5 V, unless otherwise noted) |

| Pin  | Symbol            | Rating                                  | Min | Тур | Max              | Unit |

|------|-------------------|-----------------------------------------|-----|-----|------------------|------|

| 2, 7 | V <sub>IH</sub>   | EN, TRGFL Input Digital Signal          | 1.2 |     | V <sub>BAT</sub> | V    |

| 2, 7 | VIL               | EN, TRGFL Input Digital Signal 0        |     | 0.4 | V                |      |

| 8    | V <sub>OL</sub>   | Ready Output Digital @ Irdy = 1 mA0.3   |     | 0.3 | V                |      |

| 2    | T <sub>pwfl</sub> | TRGFL Input Flash Signal Pulse Width 10 |     |     | μs               |      |

| 2, 7 | R <sub>p</sub>    | EN, TRGFL Input Pulldown Resistor       | 50  | 100 | 200              | kΩ   |

NOTE: Digital inputs undershoot  $\leq$  0.30 V to ground, Digital inputs overshoot < 0.30 V to V<sub>BAT</sub>.

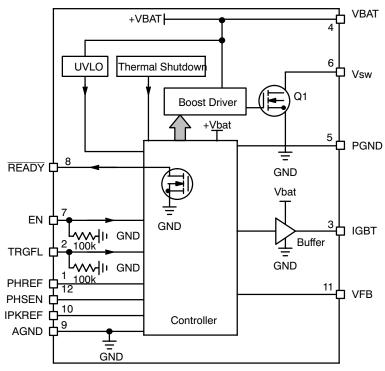

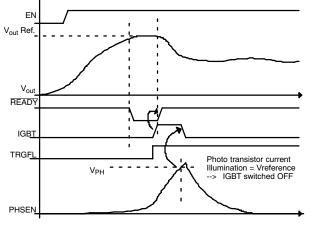

**Figure 3. Basic Operation Timings**

#### **DC/DC Operation**

The converter is based on a flyback topology, associated to an external transformer dedicated to the high voltage application. The Primary/Secondary turns ratio is defined to limit the peak voltage, at the NCP5080 pin  $V_{SW}$  level, to the operating voltage sustained by the internal NMOS device. With a 1:10 ratio, the peak voltage is limited to 30 V to

supply a regulated 300 V across the external reservoir capacitor.

Note that although an OVP circuit is built-in the NCP5080 chip, it is strongly recommended to avoid operation without an external reservoir capacitor, a 1  $\mu$ F / 315 V being the minimum value.

When the NMOS is ON, the current increases into the primary of the transformer until either the  $I_{peak}$  limit has been reached, or the time out is finished: at this point, the NMOS is switched OFF and the energy stored into the primary is dumped to the secondary, providing the current to recharge the reservoir capacitor. The OFF period is monitored by sensing the primary voltage and the system will re-start a new cycle when either  $V_p = 0$  V or the time out is finished. The external resistor divider, connected across  $V_{out}$  and Ground, senses the output voltage to close the feedback loop at FBD pin. The output voltage is based on the 1.2 V reference and the R1/R2 ratio:  $V_{out} = V_{REF} * ((R1 + R2) / R2).$

The output voltage is regulated when the EN = H, but drops to zero when EN = L. In this case, the discharge time of the external reservoir depends solely upon the value of the passive component and the leakage currents that might exist at system level.

The DC/DC converter is switched OFF when either EN = Low, or TRGFL = High, or when the output voltage has reached the programmed value (see Figure 3).

#### **Inductor Peak Current**

In order to provide more flexibility to the NCP5080 driver, an extra pin, IPKREF, is provided to set up the peak current flowing into the primary inductor of the transformer. The  $I_{REF}$  is given by the 1.14 V voltage reference and the value of the external resistor:

$$I_{REF} = 1.14 \text{ V}/\text{ RIPK} \qquad (eq. 1)$$

The primary peak current is given by Equation 1:

$$peak = I_{REF} * 14000 \qquad (eq. 2)$$

The maximum  $I_{peak}$  current shall be limited to 1.5 A maximum, assuming the transformer is sized to sustain such amount of electromagnetic energy. The efficiency of the DC/DC converter, and the recharge cycle time as well, depends upon the ESR and leakage inductance of the power transformer: a poor transformer will generate large oscillations during the operation which will be difficult to filter out at PCB level.

# Table 1. PREFERRED POWER TRANSFORMERMANUFACTURERS

| Manufacturer | Model           | Comments                           |

|--------------|-----------------|------------------------------------|

| TDK          | LDT565620ST-203 | I <sub>peak</sub> = 750 mA Max     |

| Coilcraft    | CJ5143-AL       | l <sub>peak</sub> = 1200 mA<br>Max |

| Table 2. PREFERRED HIGH VOLTAGE TRIGGER FUNCTION |

|--------------------------------------------------|

|--------------------------------------------------|

| Component                                         | Manufacturer | Model          | Comments                  |

|---------------------------------------------------|--------------|----------------|---------------------------|

| High Voltage Trigger                              | PCA          | EPC3215G-X     | V <sub>out</sub> = 4000 V |

| High Voltage Ceramic Capacitor                    | TDK          | C3225X7R2J473M | Reference design+         |

| 22 $\mu\text{F}/330$ V to 120 $\mu\text{F}/330$ V | RUBYCON      | FW series      | Preferred                 |

#### Table 3. PREFERRED XENON LAMP

| Component                     | Manufacturer          | Model                     | Comments                                               |

|-------------------------------|-----------------------|---------------------------|--------------------------------------------------------|

| Flash Lamp-Reflector Assembly | Perkin-Elmer          | RF-ASYRF160709 PKI08 (H)  | E <sub>j</sub> = 1.5 Joule<br>C <sub>out</sub> = 33 μF |

| Flash Lamp-Reflector Assembly | Perkin-Elmer          | RF-ASY RF160709 PKI07 (H) | E <sub>j</sub> = 2.1 Joule<br>C <sub>out</sub> = 47 μF |

| Flash Lamp-Reflector Assembly | Nam Kwong Co.<br>LTD. | FET-O-D03150220E-02       | 9.8 Joule,<br>C <sub>out</sub> = 180 μF                |

| Flash Lamp-Reflector Assembly | Nam Kwong Co.<br>LTD. | FET-O-D02230202A-07       | 8.0 Joule,<br>C <sub>out</sub> = 150 μF                |

#### **Perkin Elmer**

#### coordinates: kimguan.lim@perkinelmer.com

#### **Flash Strobe**

The flash is activated by the digital status present at the TRGFL Pin and the logic condition of the EN and PHSEN Pins as defined in Table 4.

| EN | TRGFL | PHREF             | PHSEN      | Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----|-------|-------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0  | Х     | Х                 | х          | System Disabled: The boost and the flash are de-activated. Any on going flash is immediately switched OFF.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1  | 0     | 0.5 V to<br>1.5 V | GND        | System Active: The output reservoir is being charged and the output voltage regulated. The photo sense is deactivated. The IGBT gate drive is LOW.                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1  | 1     | 0.5 V to<br>1.5 V | GND        | System Active: The output reservoir is being charged and the output voltage regulated. The photo sense is deactivated. The IGBT gate drive is HIGH whatever be the V <sub>out</sub> voltage value . The xenon tube is fired if V <sub>out</sub> = V <sub>xen</sub> minimum and the flash light keeps going until either TRGFL = 0, or the reservoir capacitor is fully discharged.                                                                                                                                               |  |

| 1  | 0     | VREF              | PHOTODIODE | System Active: The output reservoir is being charged and the output voltage regulated. The photo sense is activated . The IGBT gate drive is LOW.                                                                                                                                                                                                                                                                                                                                                                                |  |

| 1  | 1     | VREF              | PHOTODIODE | System Active: The output reservoir is being charged and the output voltage regulated. The photo sense is deactivated and the flash is switched OFF if the voltage present at the PHSEN Pin is higher the reference voltage applied to the PHREF Pin. The IGBT gate drive is HIGH whatever be the V <sub>out</sub> voltage value . The Xenon tube is fired if V <sub>out</sub> = V <sub>xen</sub> minimum and the IGBT keeps going until either TRGFL = 0, or the PHSEN > PHREF, or the reservoir capacitor is fully discharged. |  |

#### Table 4. FLASH OPERATING TRUE TABLE

The TRGFL signal provides a simple way to generate multiple consecutive flashes (similar to the stroboscope effect) to minimize the red eye effect, or to freeze multiple pictures of moving objects. The IGBT must be capable to turn ON with limited Gate voltage.

#### **Photodiode Sensor**

The photodiode sensor provides a feedback from the illumination generated by the xenon flash to avoid the overexposed picture. The PHREF pin shall be biased according to the model of xenon tube (in particular, the energy level) and optical lens aperture.

The function can be deactivated when not used in the application shown in Table 5. More over, connecting the PHREF Pin to the IPKREF Pin provides an easy way to fully disconnect the photo sense function.

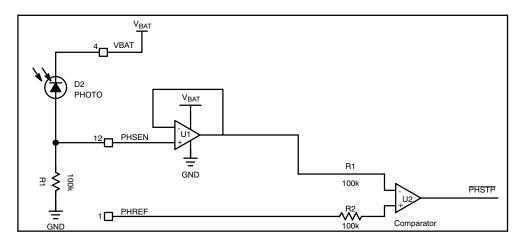

The external photo sense element shall be connected across PHSEN and  $V_{BAT}$  to source the current as the illumination increases, with a pull-down resistor connected to the ground reference as depicted in Figure 4. The sense resistor is calculated to get the collector current when the photo diode is saturated. With a typical 10  $\mu$ A to 30  $\mu$ A of photodiode current, the resistor will be 100 k $\Omega$  to cope with the low input battery supply voltage situation.

| Pin                                        | Operation                    | Operation                                                |

|--------------------------------------------|------------------------------|----------------------------------------------------------|

| $0.5 V \le PHREF \ge 1.5 V$<br>PHSEN = GND | Photodiode Sense Deactivated | The IGBT is solely controlled by the TRGFL Pin           |

| PHREF = VPH<br>PHSEN = Photodiode          | Photodiode Sense Activated   | The IGBT is controlled by the [TRGFL AND PHSEN ] status. |

Figure 4. Basic Photo Sense Input Circuit

Although it is possible to increase the photo feedback sensitivity by increasing the value of the pulldown resistor, care must be observed since such a resistor is in parallel with the internal network as depicted in Figure 4 and the input node might be too sensitive to the ambient noise. It is recommended to avoid sense resistor value above 100 k $\Omega$ , although that 1 M $\Omega$  is possible, the operation being rapidly downgraded when the resistance increases beyond this value.

The PHREF voltage is setup by the external controller, in the 0.5 V to 1.5 V range, depending upon the need of the application. The internal structure includes a 500 k $\Omega$ (typical) resistor network, connected between PHREF pin and GND : the external reference source must support such a load and a 10 k $\Omega$  output impedance, or lower, is recommended to avoid uncontrolled operation. Finally, the IGBT signal will be switched OFF when the PHSEN signal reaches the PHREF reference.

The function is deactivated by forcing a voltage in the 0.5 V to 1.5 V range at the PHREF pin, associated with a GND connection to the PHSEN pin.

Figure 5. Typical Photo Sense Timings

When the photo sense is active and the photo sense threshold has been crossed, the photo sense feedback is internally latched and recycling the TRGFL signal (H to L) is necessary to reset the latch and start a new sequence.

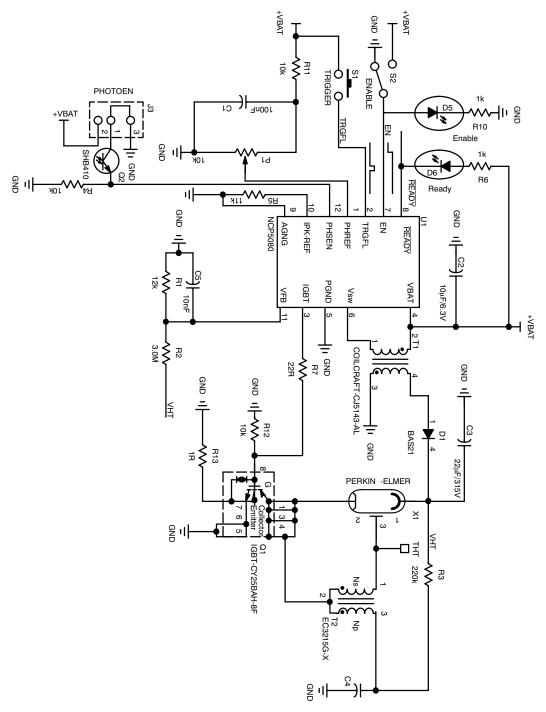

#### Simplified Flash

The circuitry can be simplified when the application does not need the multiple flashes during the same photo sequence. In this case, the IGBT can be removed as there is no more need to dynamically switch off the xenon tube . Similarly, the photo sense becomes useless since there will be no way to control the illumination once the xenon flash has been triggered. Such a feature must be properly deactivated to avoid uncontrolled operation during a photo sequence: a simple resistor network fulfill such a requirement as depicted in Figure 6.

Figure 6. Simplified Xenon Flash Controller

On the other hand, since it is not possible to connect the high voltage trigger pin to the controller (MCU or other digital device), the IGBT pin will be used to trig the SCR device necessary to fire the high voltage pulse as depicted in Figure 6.

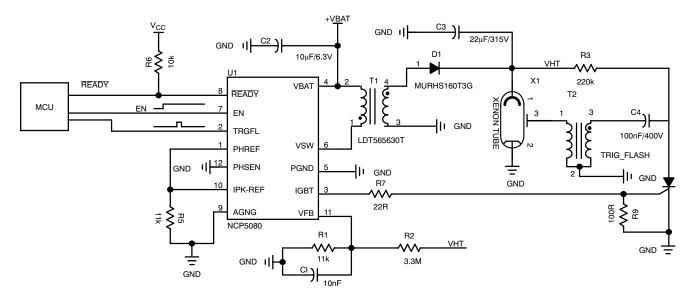

## **DEMO BOARD**

Figure 7. Demo Board Schematic Diagram

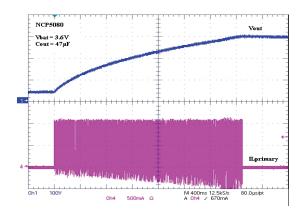

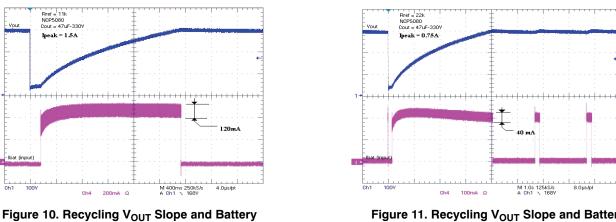

Figure 8. Output Capacitor Recharge Cycle

Input Current with Ipeak = 1.5 A

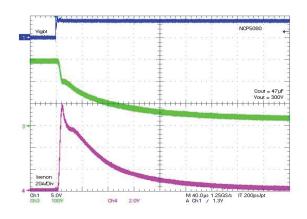

Figure 9. Xenon Tube Discharge Current

Figure 11. Recycling V<sub>OUT</sub> Slope and Battery Input Current with Ipeak = 750 mA

TRGFL: Trigger Flash pulse

You

Ibat (input)

Ch1

PHREF: photo sense reference voltage (provided by the external circuit) PHSEN: photo sense input voltage ( provided by the photo transistor sensor )

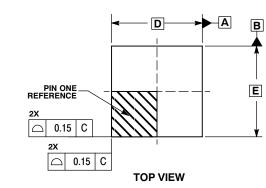

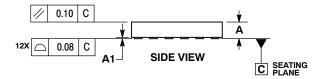

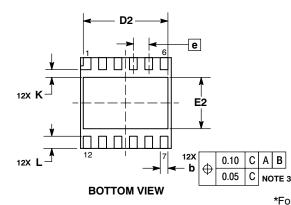

#### PACKAGE DIMENSIONS

LLGA12 CASE 513AD-01 **ISSUE A**

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 3.

- ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM TERMINAL TIP. COPLANARITY APPLIES TO THE EXPOSED DAD AS WEEL AS THE TERMINAL SPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.50        | 0.60 |  |

| A1  | 0.00        | 0.05 |  |

| b   | 0.20        | 0.30 |  |

| D   | 3.00 BSC    |      |  |

| D2  | 2.75        | 2.85 |  |

| Е   | 3.00 BSC    |      |  |

| E2  | 1.65        | 1.75 |  |

| е   | 0.50 BSC    |      |  |

| К   | 0.20        |      |  |

| L   | 0.35        | 0.45 |  |

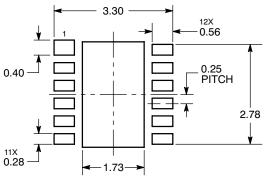

#### SOLDERING FOOTPRINT\*

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its peter frights or the rights of others. SCILLC products are not designed, intended, or authorized for use a components in systems intended for surgical implant into the body, or other applications Intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center ON Semiconductor Website: www.onsemi.com Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Phone: 81-3-5773-3850

Sales Representative